0510-81135862

半导体 IC, 分离器件 (Discrete device), LED 及其他各类电子元件及 Assembly board, 模组等相关产品

在生产制造、运输、组装、使用过程中容易受到 ESD 冲击, ESD 抗扰度是保证产品可靠性的重要因素。

。下面将半导体装置实际会经历的多种状况做成模型化,可按每个试验水平将产品ESD耐性(sensitivity)分为几个等级。(分类)

该试验假设“半导体”与“人体”是经过多种方式取得电荷或失去电荷的两种物质。

准备一个模仿人体特性的电路,向半导体施加ESD pulse。HBM分类水平为250 V ~ 8000 V。

该试验虚拟营造半导体生产工程中通过与设备或其他金属的摩擦,充电荷后再接触其他物质时发生的ESD现象。MM分类水平为50 V ~ 400 V。

是最接近于Field不良的试验。

该试验利用向Package充电荷的方法。CDM分类水平为200 V ~ 1000 V。

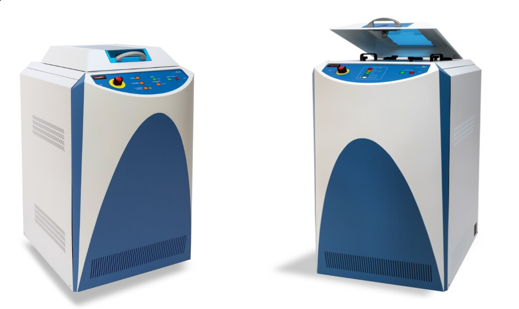

配置业内 的ESD测试机MK2/MK4设备

MK4 可支持测试2304通道

HBM测试可达±30V~8000V

实时IV曲线跟踪

拥有多种规格 Socket Boards

专业工程师亲自测试,高效,准确

快速测试,收到样品后48小时内反馈结果

免费提供CNAS报告,无任何追加费用

CNAS认证范围广,覆盖MIL-STD-883, GJB-548C,AEC-Q100, AEC-Q101,JS002&JS001,JESD-78 等

MK2.SE/ ThermoFisherScientific MK4.TE /Thermo Fisher Scientific

Latch-up试验:像CMOS这样的元件不可避免地形成p-n-p-n结构,在这种结构下形成的寄生者(parasitic) Thyristor在某种电的影响下工作,电流通过、放大破坏元件的实验方法。

Test Pin count : 2304(MK4), 768(MK2)

Latch-up Vector : 256k depth/20MHz(MK4),

64k depth/10MHz(MK2)

Power Supplies : 8 separate V/I(MK4),6 separate V/I(MK2)

寄生thyristor引起latch-up。

JJESD22-78 “Latch-up”

研究分析EOS故障的事例

当直接电路或电子配件对浪涌(surge)造成影响时,对此可以设定一般的允许标准。该试验根据最终试验结果表明的每个试验PIN组合和对极性的最少保证水平,可以决定每个EOS浪涌的IC允许程度。

| 合成波形 | 试验次数 | |

|---|---|---|

| 开路电压(OCV) | 短路电压(SCC) | |

上升:1.2㎲ ± 20% 持续时间:50㎲ ± 30% |  上升:8㎲ ± 20% 持续时间:20㎲ ± 30% | 3 次 |

EOS 脉冲规格 (IEC 61000-4-5)