带电器件模型(CDM)测试介绍

带电器件模型

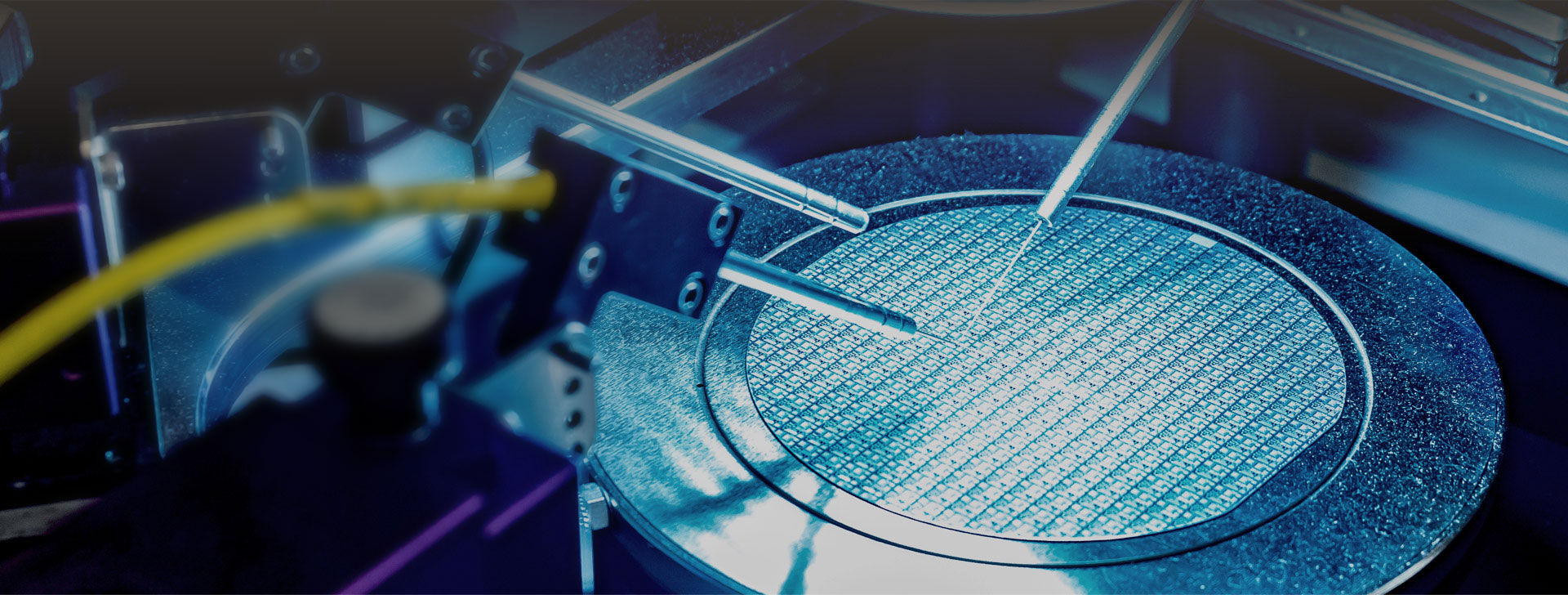

评估电子元器件对静电放电耐受能力的测试

测试介绍

本试验是模拟半导体及电子元器件因摩擦、接触等原因,相应元器件的电荷被积累(充电),充电的元器件与导体接触时,发生急剧放电现象的一款试验。ESD只要能体现No charge(不充电)或 No discharge(不放电)环境,就不会引发任何不良。但根源上消除静电不可能的,因此要评估IC和电子元器件的耐性水平。

适用技术

可对半导体(Memory,Sysetm IC),Discrete IC(分立器件),无源器件Level ESD(CDM)试验,板级CBM(Charged Board Model)进行试验

| 参考规范 | |

|---|---|

| AEC-Q100-011-REV-D:2019 | AEC-Q101-005-REV-A: 2019 |

| JESD22-C101F:2013 | ANSI/ESDA/JEDEC JS-002-2022 |

| AEC-Q100-REV-J:2023;Table 2,Test group E3,CDM | AEC-Q101-Rev-E:2021;Table 2,Test group E4,ESDC(ESD CDM Characterization) |

| AEC-Q104-Rev:2017;Table 1,Test group E3,CDM | |

- 上一个:人体放电/机械模式静电放电

- 下一个:闩锁效应